隨著摩爾定律逐漸逼近物理極限,集成電路(IC)設計正步入一個以創新探針未來趨勢的關鍵時期。未來的IC設計將不再僅僅追求晶體管密度的單純提升,而是轉向多維度的技術融合與范式革新,其發展趨勢主要體現在以下幾個核心方向。

一、異構集成與先進封裝成為新引擎

傳統的單芯片SoC(片上系統)設計正面臨功耗、性能和成本的多重挑戰。通過2.5D/3D封裝、Chiplet(芯粒)等技術實現的異構集成將成為主流。設計重點將從單一晶粒轉向多芯片模塊的協同優化,利用硅中介層、微凸塊等技術實現內存、邏輯、模擬/RF芯片的高密度互連。這不僅延續了性能提升的路徑,還大幅降低了先進制程的研發成本和風險,使得設計公司能夠更靈活地組合不同工藝節點的IP,實現定制化、高效能的系統解決方案。

二、EDA工具全面智能化與云端化

電子設計自動化(EDA)工具是IC設計的基石。EDA將深度融入人工智能(AI)和機器學習(ML),實現設計流程的自動化與最優化。AI將應用于從架構探索、邏輯綜合、布局布線到物理驗證的全流程,大幅縮短設計周期并提升芯片首輪成功率。EDA云端化平臺將為企業,特別是中小企業,提供彈性的、高性能的計算資源與協同設計環境,降低基礎設施投入,并加強數據安全和設計IP的管理。

三、面向特定領域(DSA)與軟硬件協同設計

通用處理器(CPU)的性能增長放緩,促使針對人工智能、自動駕駛、物聯網、高性能計算等特定領域的架構(DSA)蓬勃發展。未來的IC設計將更緊密地與算法、軟件棧乃至應用場景綁定。通過軟硬件協同設計,在架構層面進行定制化優化(如定制指令集、專用計算單元、近內存計算),以達成極致的能效比。這要求設計團隊具備跨領域的系統級視角,芯片將成為承載垂直領域解決方案的核心載體。

四、新材料與新器件結構的探索

為突破硅基CMOS的瓶頸,新材料(如二維材料、氧化物半導體)和新器件結構(如環柵晶體管GAA、CFET互補場效應晶體管)將從研究走向量產。這給IC設計帶來了新的機遇與挑戰:設計規則、器件模型、可靠性評估方法都需要革新。設計人員需要理解這些新器件的物理特性,并與工藝團隊緊密合作,開發新的設計方法和IP庫,以釋放其性能潛力。

五、安全性、可靠性與可持續性成為設計核心考量

隨著芯片滲透到社會生活的方方面面,其安全性和可靠性變得至關重要。未來的設計必須在架構層面內置硬件安全模塊(HSM)、側信道攻擊防護、可信執行環境(TEE)等。在汽車電子、工業控制等領域,功能安全(如ISO 26262)設計標準將更加嚴格。從設計源頭考慮能效、碳足跡和可回收性的“綠色芯片”理念也將興起,推動低功耗設計技術和環保材料的應用。

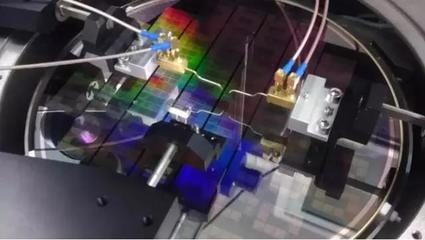

六、系統級與光子/電子融合設計

未來的復雜系統可能是芯片、封裝、板級甚至光互連的混合體。硅光子學技術成熟,使得在芯片上集成光通信器件成為可能,以應對數據中心內部高速互連的帶寬和功耗挑戰。這要求IC設計師具備光-電-熱多物理場協同設計的知識,實現光電共封裝(CPO)等先進架構。

集成電路設計的未來是一個從“制造驅動”轉向“架構與系統創新驅動”的深刻變革。它要求設計生態(設計公司、EDA廠商、代工廠、IP供應商)更緊密地協作,并培養具備跨學科知識的復合型人才。成功的設計將不再是晶體管的簡單堆砌,而是在性能、功耗、成本、上市時間和多功能集成之間取得精妙平衡的系統工程,最終為智能社會的各個角落提供強大的數字心臟。