在電子工程與集成電路設計領域,對特定功能集成電路(IC)進行快速、準確的測試是產品研發、生產調試及維修保障的關鍵環節。傳統通用測試設備往往成本高昂、操作復雜,而針對特定芯片定制專用測試儀則能顯著提升效率與便捷性。本文探討一種基于經典八位單片機AT89C55為核心控制器,設計并實現一款面向特定集成電路的簡易、低成本測試儀的方案。

一、系統總體設計方案

本測試儀的核心設計思想是利用89C55單片機強大的I/O控制能力、定時器/計數器以及可編程特性,模擬待測集成電路所需的工作時序和輸入激勵信號,同時采集其輸出響應,并與預存的正確響應數據進行比對,從而判斷集成電路功能是否正常。

系統硬件主要由以下幾個模塊構成:

- 主控模塊:以AT89C55單片機為核心,負責整個測試流程的控制、信號生成、數據采集與結果判斷。其內部32KB的Flash ROM足以存儲復雜的測試程序和多組測試向量。

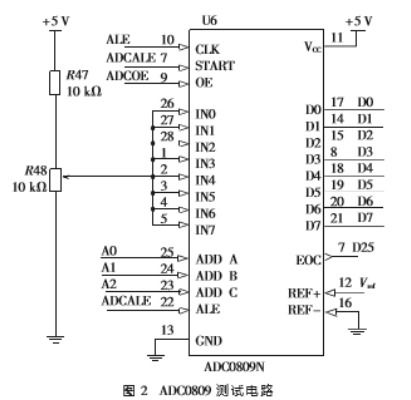

- 信號接口與驅動模塊:根據待測集成電路的引腳定義,設計對應的接口電路。包括電平轉換電路(如使用74HC系列芯片確保TTL/CMOS電平兼容)、必要的驅動電路(以提供足夠的電流驅動能力)以及保護電路(如限流電阻)。

- 人機交互模塊:通常包括一個簡單的鍵盤(用于選擇測試項目、啟動測試)和一塊LCD顯示屏(用于顯示測試進度、結果“PASS/FAIL”或詳細的錯誤信息)。

- 電源模塊:為單片機、待測芯片及其他外圍電路提供穩定、純凈的直流工作電壓,需注意電壓值與待測芯片要求嚴格匹配。

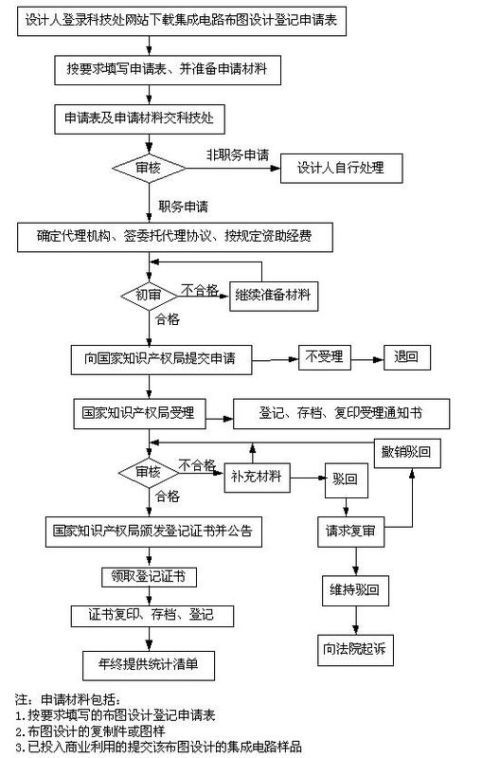

二、關鍵軟件設計流程

軟件是測試儀的靈魂,其設計直接決定了測試的準確性與可靠性。程序采用模塊化設計,主要流程如下:

- 初始化:配置89C55的I/O口模式(部分引腳設置為輸出以產生激勵,部分設置為輸入以讀取響應)、初始化定時器、LCD顯示屏等。

- 測試向量加載:從程序存儲器中讀取針對該特定集成電路的測試向量集。測試向量包含了在特定時鐘序列下,需要施加到各輸入引腳的邏輯狀態(0或1)以及預期從各輸出引腳讀回的邏輯狀態。

- 激勵信號施加與響應采集:單片機按照測試向量定義的時序,通過其I/O口將激勵信號施加到待測IC的對應引腳。在規定的建立時間和保持時間后,單片機讀取待測IC輸出引腳的實際狀態。

- 結果比對與判斷:將采集到的實際輸出與測試向量中的預期輸出進行逐位比對。若所有位在允許的容差范圍內(對于數字電路通常是完全一致)均匹配,則判定該組測試通過;否則,記錄失敗信息。

- 結果輸出與顯示:完成所有測試向量組的測試后,綜合判斷該集成電路是否合格,并將最終結果(“通過”或“失敗”,必要時包括失敗的具體引腳或測試項)顯示在LCD上。

三、針對特定集成電路的設計考量

“特定集成電路”意味著測試儀的設計不是通用的,而是高度定制化的。在設計中需重點考慮:

- 引腳映射:精確定義89C55的每個I/O口與待測IC引腳的對應關系。

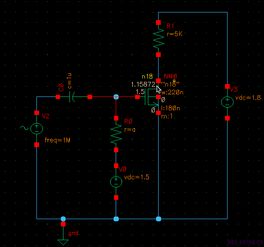

- 時序模擬:仔細分析待測IC的數據手冊,用單片機的定時器和軟件延時精確復現其工作所需的時鐘頻率、脈沖寬度、建立/保持時間等關鍵時序參數。

- 測試向量的生成:測試向量的完備性直接影響測試覆蓋率。需要基于待測IC的功能真值表、狀態圖或已知的故障模型,生成能夠充分驗證其邏輯功能的測試序列。這部分工作往往需要借助電路仿真軟件(如Proteus)或專門的測試生成理論輔助完成。

- 容錯與保護:程序中應加入超時判斷、短路檢測等容錯機制,硬件上需考慮對過流、靜電等意外情況的防護,以保護昂貴的待測芯片和測試儀本身。

四、實現優勢與局限

優勢:

- 成本極低:核心元件89C55單片機及其外圍電路成本遠低于商用測試儀。

- 靈活專用:通過更改軟件和接口適配,可以快速適配不同型號的特定IC,開發周期短。

- 操作簡便:通常一鍵測試,結果直觀明了,適合生產線或維修點使用。

局限:

- 測試速度:受限于8位單片機的處理速度,測試頻率通常不高,難以測試高速IC。

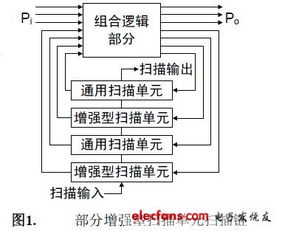

- 測試復雜度:對于引腳眾多、時序極其復雜或模擬混合信號的IC,僅用單片機實現難度大,可能需要加入CPLD/FPGA或專用模擬開關等輔助芯片。

- 精度限制:在需要高精度電壓、電流或時間測量的場合,此簡易方案精度有限。

###

基于AT89C55單片機設計特定集成電路測試儀,是一種在成本、效率與功能之間取得良好平衡的實用方案。它充分展現了通過簡潔的嵌入式系統解決特定工程問題的設計思路。對于數字邏輯電路、簡單的接口芯片(如鎖存器、譯碼器、特定型號的ROM等)的功能驗證,該方案具有顯著的實用價值。隨著單片機性能的提升和設計工具的完善,此類專用測試儀的設計將更加高效與強大,成為集成電路設計與應用領域中不可或缺的輔助工具。